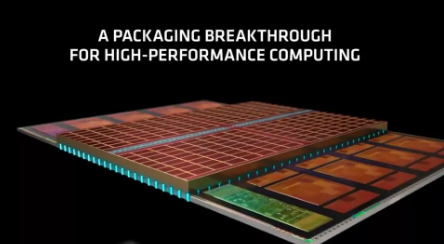

AMD 几个月前宣布了其 3D V-Cache 技术,通过在 Ryzen CPU 之上简单地堆叠更多 L3 缓存(高达 64MB),展示了令人难以置信的性能提升。现在,感谢来自 TechInsights 的 Yuzo Fukuzaki,我们有了更多与 3D V-Cache 相关的细节。这包括显示现代 Zen 3 CPU 从一开始就设计用于容纳堆叠 3D 缓存的数据,这告诉我们这项技术已经投入使用多年。

据 Fukuzaki 称,他在标准的 Ryzen 9 5950X 样品上找到了连接点和 3D 堆栈缓存空间。查看下图,您可以看到 Zen 3 芯片边缘的点,可以连接 3D V-Cache。如果要安装另一个 3D 缓存堆栈,这些是铜质连接点。

TechInsights 3D V-Cache 发现

此安装过程使用 TSV(硅通孔)通过混合键合将第二层 SRAM 固定到芯片上。由于 TSV 使用铜而不是焊料,因此与简单地将芯片焊接在一起相比,SRAM 具有更高的带宽和热效率。

根据他们的分析,该公司对 3D V-Cache 连接方式背后的一些细节进行了逆向工程,包括 TSV 间距、CPU 内部用于另一个缓存堆栈的空白空间等等。

TSV工艺位置;M10-M11之间(共15种金属,从M0开始)

标签: AMD